NextInfo.hu, 2022/3/22

A Milan-X" 3D függőleges gyorsítótár az Epyc HPC-hez képest nagyobb teljesítményt biztosít. Tavaly ősszel az SC21 szuperszámítógépes konferencia előtt az AMD közölte, hogy a nagy számítási motorgyártók közül elsőként 3D-s függőleges L3 gyorsítótárat ad a chipjeihez, ebben az esetben a 2021 márciusában debütáló "Milan" Epyc 7003-as sorozat "Milan-X" néven futó processzorainak változataihoz.

És ma, közvetlenül az Nvidia GPU éves technikai konferenciájának kezdete előtt az AMD ünneprontó játékot játszik, és négy vastag gyorsítótárral ellátott Milan-X változatot ad a harmadik generációs Epyc 7003-as CPU-sorozathoz. A 3D-s függőleges L3 gyorsítótárak processzorkomplexumhoz való hozzáadásának technikája nagyon érdekes, és ízelítőt ad arról, hogy a közeljövőben hogyan lehet a chipek ingatlanjait jobban kihasználni mindenféle chipekben.

És úgy gondoljuk, hogy a számítómotorok létrehozására használt chipek nem csak 2D-sek vagy akár 2,5D-sek lesznek, hanem egyre inkább 3D-s elemeket is tartalmaznak majd - eleinte nem a komplexum minden elemét, jól jegyezzük meg. De ilyen módon a számítási motorok egyre kevésbé hasonlítanak a külvárosokhoz, és egyre inkább a nagyvárosokhoz - és mint kiderült, nagyrészt ugyanazokból a gazdasági és időbeli okokból, amelyek a városokat is arra késztetik, hogy az ég felé nyúljanak.

Amint arról korábban már beszámoltunk, a Milan-X processzor az AMD azon igényét képviseli, hogy diverzifikálja CPU-, GPU- és most már FPGA-kínálatát, hogy minél nagyobb részesedést szerezzen a számítási motorok piacából, amely egyre sokszínűbbé válik, ahogy Moore törvénye kifogy a benzinből, és a hardvereket konkrét munkaterhelésekre kell szabni.

Legalábbis úgy gondoljuk, hogy jó esély van arra, hogy a jövőben minden CPU- és talán még GPU-generációból is lesznek "X" változatok, amelyek 3D V-Cache-t tartalmaznak. De a függőleges L3 gyorsítótár-megközelítés a szerver CPU-aljzat két dimenziójában is több területet nyithat meg, így több mag vagy nagyobb I/O-dobozok hozzáadására lehetne használni a számítási komplexumban.

De ez egy másik nap témája. Egyelőre arra szeretnénk koncentrálni, hogy az AMD hogyan építette fel a 3D-s függőleges L3 gyorsítótárat a Milan-X változatok esetében, milyen új SKU-kat tartalmaz a Milan termékcsalád X jelöléssel, és hogyan viszonyulnak a lapkák a hagyományos Milan CPU-komplexumokhoz. Az Intel "Ice Lake" Xeon SP processzorokkal szembeni teljesítményelemzést egy következő cikkben fogjuk elvégezni.

Nagy függőleges ugrás

Ebben az esetben a Milan-X chipek célja az elektronikai tervezés automatizálásának, a számítási áramlástan, a végeselemes analízis és a szerkezeti analízis szimulációk teljesítményének növelése - mint kiderült, ezek mindegyike nagyon jól skálázza teljesítményét, ha extra L3 gyorsítótárat kap, hogy a processzorok egy CPU-ban elfoglalva legyenek. "Ez nem egy kalapács, amely szöget keres" - magyarázza Sam Naffziger, az AMD vállalati munkatársa és terméktechnológiai architektje.

"Ez egy nagyon jól átgondolt, stratégiai terv arra, hogy szerverprocesszorainkat sokkal versenyképesebbé tegyük, és sokkal nagyobb teljesítményt nyújtsunk."

A Moore-törvény lassulása a számítási motor különböző részeit különbözőképpen és különböző időpontokban érte, és Naffziger még azelőtt ismertette a helyzetet, hogy belemerült volna a 3D V-Cache felépítésének részleteibe, és mielőtt Ram Peddibhotla, az AMD adatközponti termékekért felelős vállalati termékmenedzsment alelnöke beszélt volna a négy új Milan-X SKU-ról, és elég betekintést adott ahhoz, hogy kiszámolhassunk néhány relatív teljesítményértékelést a Milan és a Milan-X között a négy HPC-munkaterhelésre, amelyeket a Milan-X céloz.

"A gyorsítótárak csodálatos dolgok - folytatta Naffziger. "Nagyon alacsony energiaigényű, alacsony késleltetésű helyi tárolót biztosítanak, amely sok alkalmazás esetében kiszolgálja a sávszélességre vonatkozó igényeket. A chipen kívülre, a memóriába vagy a lapkán kívülre, más tárolóeszközökhöz való átmenet sok energiába és késleltetésbe kerül."

Közvetlen összefüggés van a gyorsítótár növekvő mérete és a CPU-magok órajelenkénti utasításainak (IPC) növekedése között. A probléma azonban az, hogy az L3 gyorsítótárak készítéséhez használt SRAM méretezési üteme lassul, ahogyan az a CPU-komplexum I/O-részeinek (amelyek a memóriavezérlőket és más I/O-vezérlőket tartalmazzák) esetében is történt néhány évvel ezelőtt, amint az a diagram jobb oldalán látható. A számítási komplexum logikai része - a magok és azok L1 és L2 gyorsítótárai - ehhez képest elég jól skálázódtak.

Az a tény, hogy az analóg, digitális és SRAM komponensek eltérő ütemben skálázódnak - pontosabban különböző időpontokban ütköztek a Moore-törvény falába - az oka annak, hogy az AMD olyan chiplet-architektúrára váltott, amely a memória- és I/O-diét 14 nanométeres, majd 12 nanométeres eljárásra helyezte, és a magdobozokat 14 nanométeres, majd 7 nanométeres eljárásra szorította. Míg az SRAM "szépen skálázódott" a 7 nanométeres csomóponton, Naffziger szerint a jövőre nézve "leesik a görbéről".

Ráadásul az egyre nagyobb és nagyobb L3 gyorsítótár hozzáadása bármely processzorhoz saját kihívásokkal jár. Ha az AMD meg akarja duplázni vagy megháromszorozni az L3 gyorsítótárat egy számítási komplex die-n (CCD), akkor az a chiplet sokkal nagyobb lesz, ami csökkenti az adott helyen belül a magok számára rendelkezésre álló területet. Egy chip hozama némileg arányos a méretével, így a nagyobb chipek hozama is alacsonyabb lenne, ami kihat a chip költségére.

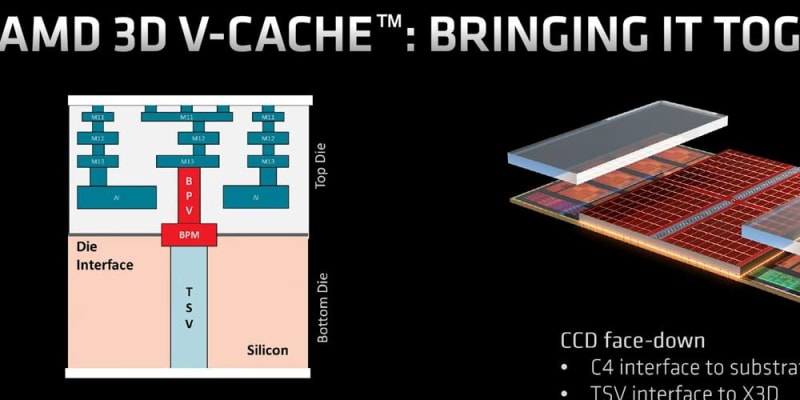

Végül pedig az L3 gyorsítótár két dimenzióban történő megnövelése azt jelenti, hogy a gyorsítótáron átívelő távolság nagyobb, ami növeli a gyorsítótár késleltetését, és így ténylegesen akadályozhatja a számítási motor teljesítménynövekedését. Az AMD ezért a Taiwan Semiconductor Manufacturing Co-val együttműködve dolgozta ki a 3D V-Cache-t. Éjszaka azt gondolhatod, hogy a 3D V-Cache-sel az AMD csak lemásolja ugyanazokat az L3 gyorsítótár szegmenseket, amelyek a Milan CCD-n vannak, és kétszer két rétegben beilleszti a CCD-k fölé, majd szilícium átvezetőkön (TSV-ken) keresztül összekapcsolja őket, hasonlóan ahhoz, ahogyan a DRAM-ot is TSV-k segítségével rakják egymásra és kapcsolják össze a GPU gyorsítókban és most már néhány CPU-ban általánosan használt HBM memóriához. De ez nem így működik, és az AMD ennél sokkal okosabb volt.

Az AMD fogta a Milan CCD-k L3 gyorsítótárának kialakítását, és teljesen eltávolította a gyűrűs buszt, hogy létrehozza az X3D függőleges gyorsítótár szegmenst. És amikor ezt megtette, az AMD kétszer olyan sűrűvé tudta tenni a függőleges L3 gyorsítótár memóriát. (A busz és a címkék ennyi ingatlant fogyasztanak, ami számunkra meglepő volt.) A Milan die-ből a CCD-n lévő 32 MB L3 gyorsítótárból felfelé mutató jel TSV-k a kezdetektől fogva ott voltak (a sima vaníliás Milan chipeken sötét szilícium).

A 64 MB X3D L3 gyorsítótár kiegészítőből lefelé mutató jel TSV-k tökéletesen illeszkednek a Milan chip felfelé mutató TSV-ihoz, és kémiai úton, rézből rézbe vannak hegesztve, hibrid kötési technikával, így: Az Epyc 7003 csomagban lévő Milan CCD magok szempontjából a függőleges L3 gyorsítótár szegmenshez való késleltetés lényegében megegyezik a Milan CCD L3 gyorsítótárához való késleltetéssel. (Ez zseniális.)

A 3D V-Cache csak a Milan CCD gyorsítótár-szegmensek fölé rakható, és fűtési és hűtési okokból nem rakható a CCD-magok fölé. És tekintve a 3D-s átállás által biztosított egységes késleltetést, a Milan CCD-ken lévő gyűrűs busz megosztásának köszönhetően, ezt nem is szeretné másképp csinálni. A CCD-knek a Milan-magokat tartalmazó részeihez oxidkötéssel vannak rögzítve a szerkezeti dummy süllyesztékek, így a hőátadás a Milan-X csomag feletti hűtőbordákig változatlan marad.

A Milan-X szerszámok terheléstől függően 225 watt és 280 watt közötti teljesítményt vezetnek le, a 280 wattos érték a "római" Epyc 7002 és Milan Epyc 7003 processzorokkal használt SP3 foglalatnál megengedett felső határérték. A Milan-X chipek 3D V-Cache-je egy BIOS-frissítéssel engedélyezhető, ami nagyszerű az OEM-ek és ODM-ek számára, akik nem akarnak új alaplapokat vagy rendszereket minősíteni a Milan-X processzorok használatához.

Az L3 gyorsítótár memória sávszélessége, több mint 2 TB/sec, nem változott, mivel az L3 gyűrűs busz szerkezete nem igazán változott a függőleges gyorsítótár hozzáadásával. A Milan-X a hagyományos Milan lapkákhoz hasonlóan lehetővé teszi, hogy az összes L3 gyorsítótárat egyetlen aktív maghoz rendeljék, ha ez tetszik.

Az Epyc 7003-as sorozat négy Milan-X lapkája félkövér, piros dőlt betűvel van szedve. Az AMD megismételte, hogy a Synopsys VCS EDA eszközén, egy meg nem nevezett AMD grafikus kártyával végzett szimulációt futtatva a 16 magos Milan-X chip, az Epyc 7373X 66 százalékkal több RTL verifikációs feladatot végzett egy óra alatt, mint a normál 16 magos Milan-X chip, amely feltételezésünk szerint az Epyc 73F3 néven ismert HPC változat volt. De novemberben, amikor a Milan-X chip előzetese bemutatásra került, az AMD azt mondta, hogy a Milan-X chipek átlagosan 50 százalékos teljesítménynövekedést biztosítanak a Milan-egyenlőkhöz képest. Így hát 1,5-szeres szorzóval számoltuk a Milan-X és a Milan F sorozatú rokonuk (ahol van ilyen) közötti relatív teljesítményt.

Mint látható, sok esetben a Milan-X magjainak órajele lelassult a legközelebbi egyenértékű Milan lapka sebességéhez képest, ami csökkenti a nyers teljesítményt, majd az L3 gyorsítótár megháromszorozásával a Milan-X lapka összteljesítménye jóval előrébb kerül, anélkül, hogy a gyorsítótár késleltetési idejét növelné. A chipeken a Milan-X wattjai megegyeznek a Milan megfelelőivel, do ez a teljesítménynövekedés egyenesen 50 százalékos wattonkénti teljesítménynövekedésként megy át; a másik két Milan-X chipen.

A nettó hatás tehát az, hogy még a Milan-X-re való átállás esetén is 10,8 százaléktól 34,5 százalékig terjedő áremelkedés mellett - a Milan-X SKU-tól függően - az ár/teljesítmény 20,8 százalékkal 25,6 százalékkal javul a három Milan-X SKU esetében. Az Epyc 7473X a teljesítménynövekedéshez képest kissé drága, és az ár-érték arány csak 10,3 százalékkal javul. Mondja meg az AMD, hogy az Epyc 7473X árát 700 dollárral 3200 dollárra, az Epyc 7373X árát pedig 200 dollárral 3185 dollárra csökkentse, és minden tökéletesen összeáll, ha ár/teljesítményről van szó.

Itt van egy érdekes információ, amit Peddibhotla megosztott arról, hogy a Milan-X SKU-k milyen munkaterheléseket céloztak meg, és ennek van értelme, ha belegondolunk, hogy bizonyos HPC-munkaterhelések mennyire érzékenyek nemcsak az L3 gyorsítótárra, hanem az órajelsebességre is. Még egy utolsó dolog, amikor a Milan-X chipeket vizsgáljuk. Ha fogunk egy Milan-X-et, és másfajta munkaterhelést alkalmazunk vele, olyanokat, amelyek nem annyira érzékenyek az L3 gyorsítótár méretére, akkor sokkal rosszabb eredményt kapunk a pénzünkért.

Az órajelek lassabbak lesznek, a chip pedig drágul, és az ár/teljesítmény nettó vesztesége drámai lehet. Ezt a Milan családon belül a fenti táblázatban szereplő nyers összesített órajelciklusonkénti költség mérőszám segítségével lehet felmérni, amely nem veszi figyelembe a generációk közötti IPC-változásokat, és amely nem tartalmazza a 3D V-Cache növelésének hatását a fent vázolt négy HPC-munkaterhelésre.

Ne feledje, hogy a mi relatív teljesítményünket a 2,8 GHz-en futó, négymagos "Shanghai" Opteron 2387-es processzor teljesítményéhez viszonyítottuk, amely mindössze 6 MB gyorsítótárral rendelkezett, és amely 2008 novemberi megjelenésekor mindössze 873 dollárba került. A Milan-X lapkák összehasonlítását a Shanghai lapkákkal, valamint a két korábbi Naples Epyc 7001 és a Rome Epyc 7002 processzorokkal itt nézheti meg.